今回のコラムでは、プレーン共振の抑制方法を紹介します。

ノイズ源の一つ:プレーン共振

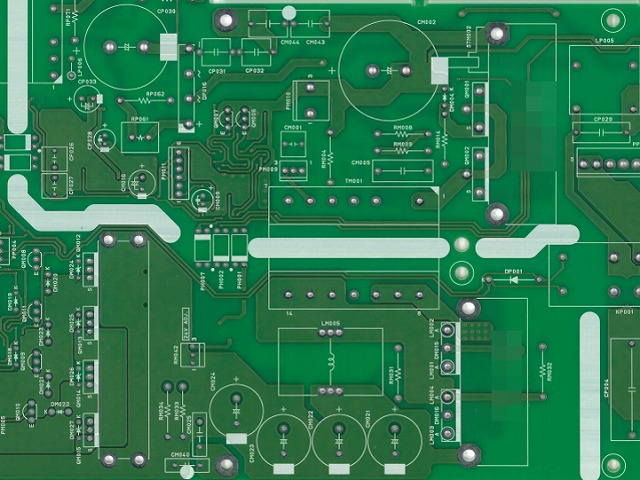

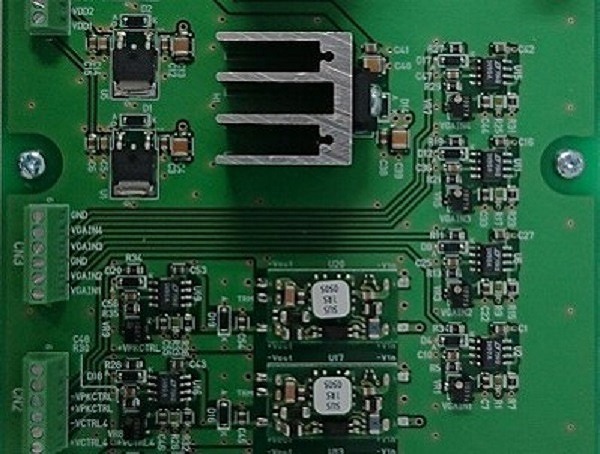

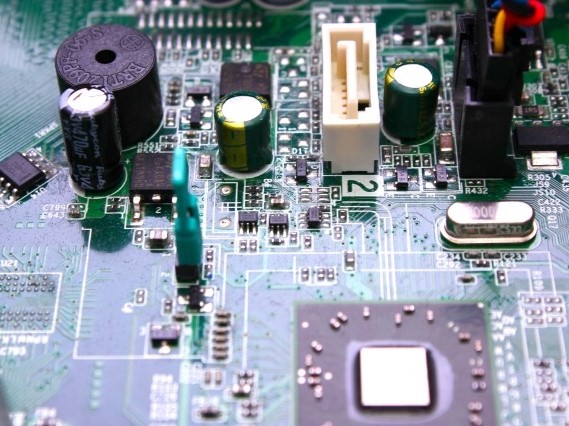

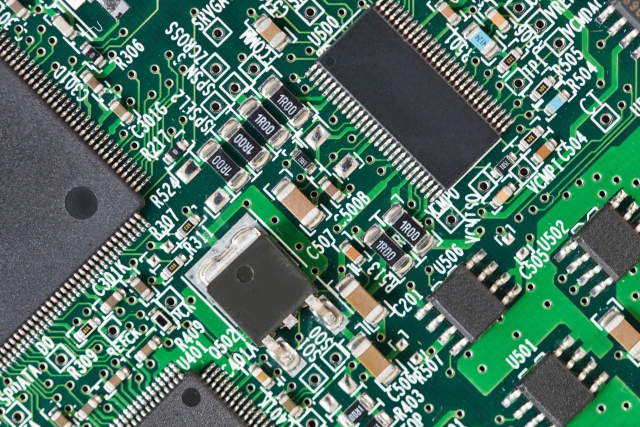

電子部品を搭載したプリント基板は様々なノイズの発生源となっていますが、その中でも大きなノイズ源の一つとされているのがプレーン共振によるものです。

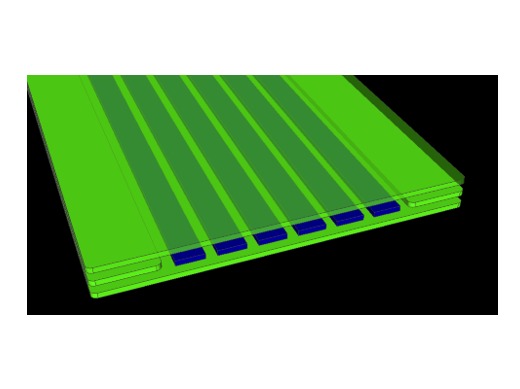

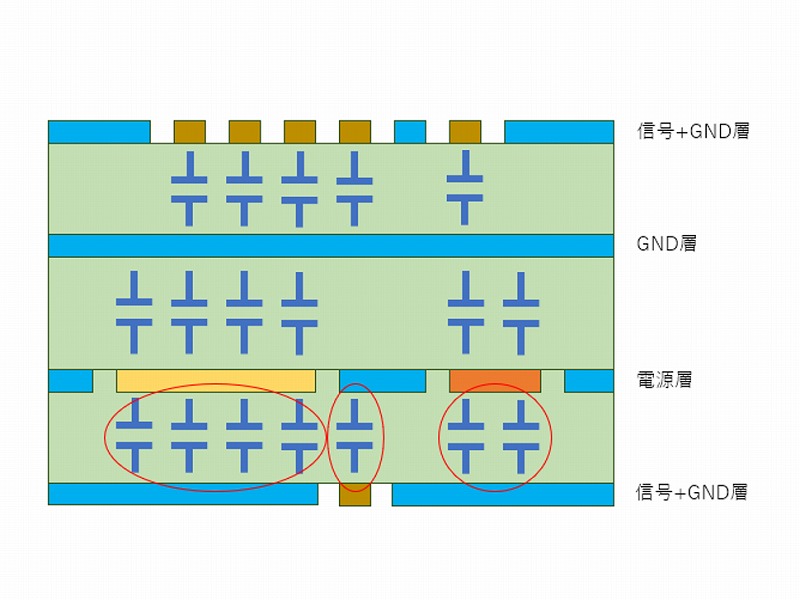

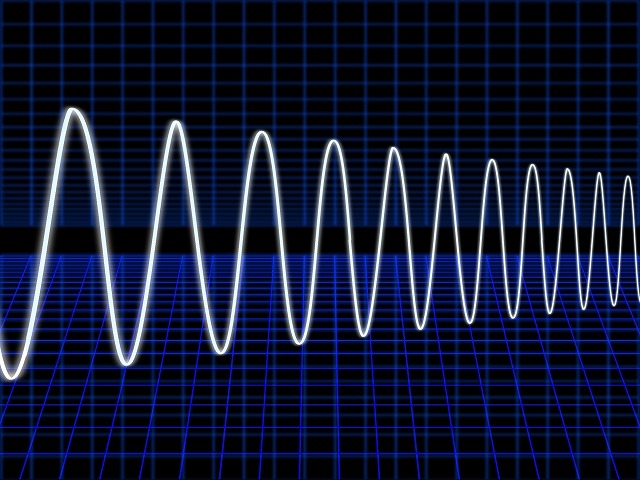

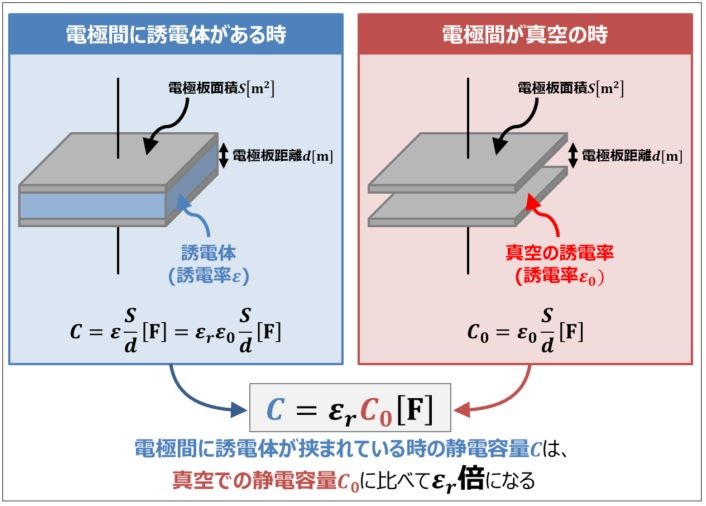

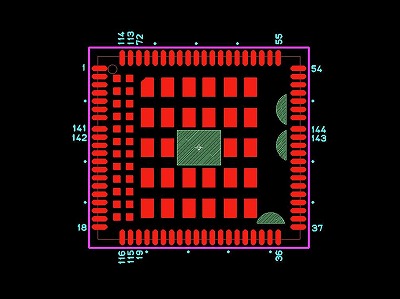

プリント基板上で貼られた電源プレーン(面)とGNDプレーン(面)が平行平板のような形になり、電源プレーンの端で発生したノイズの反射波が重なり合った結果、電源プレーン内の特定箇所のノイズ量が極端に高くなる現象が起きますが、これをプレーン共振といいます。

各プレーン間に接続される回路/配線などの要因によって、それぞれのプレーンが重なっている箇所でプレーン共振が励振されるイメージになります。

プレーン共振によって生じる問題

プレーン共振によって生じる問題は主に下記の3点です。

・基板外に影響を及ぼすEMI(電磁妨害)の放射ノイズの増大

・プレーン上に配置したチップICのノイズマージンの不足

※入力信号の変動や周囲のノイズに対し回路が安定して動作するための余裕が減ることにより、ICの信号の読み取り/出力の精度が下がります。

・コモンモードノイズの発生

プレーン共振の対策

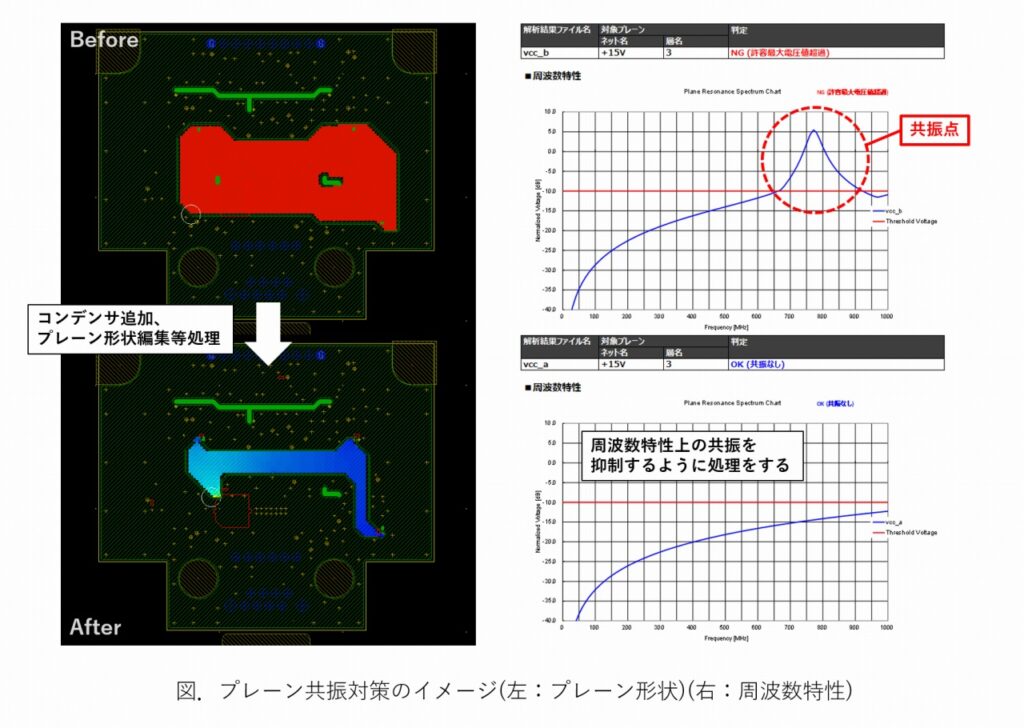

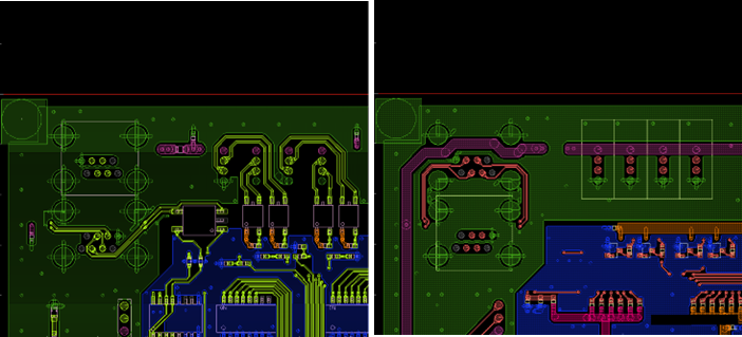

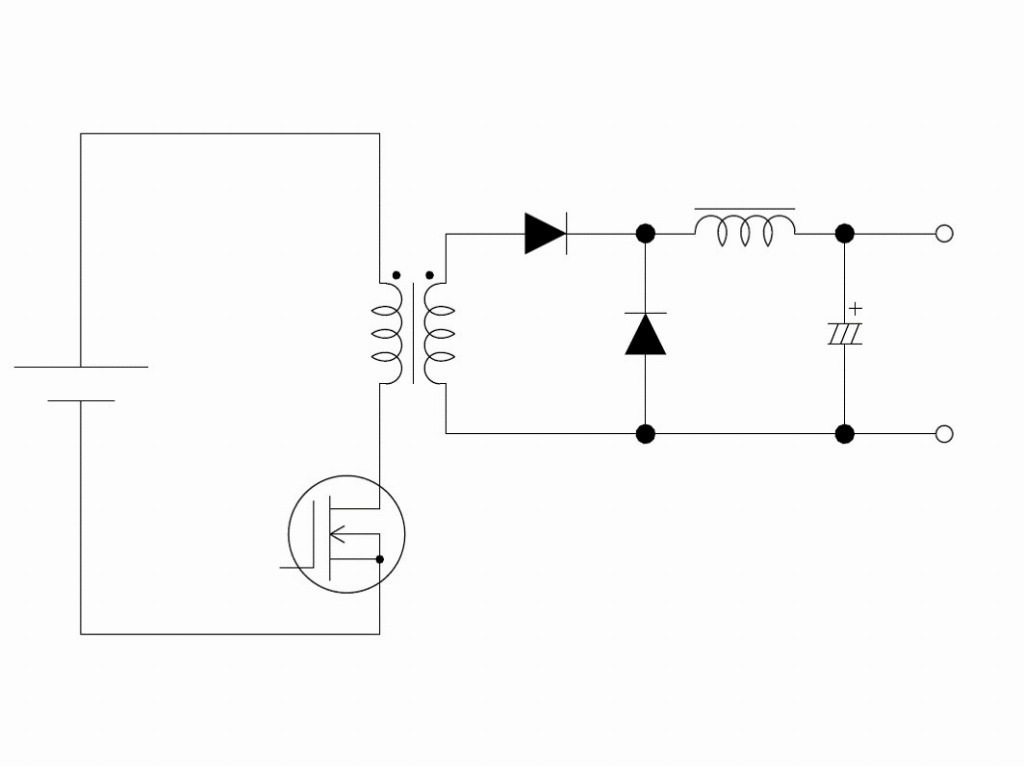

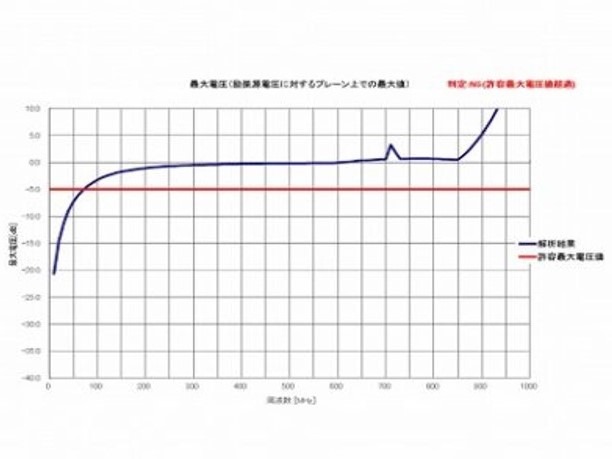

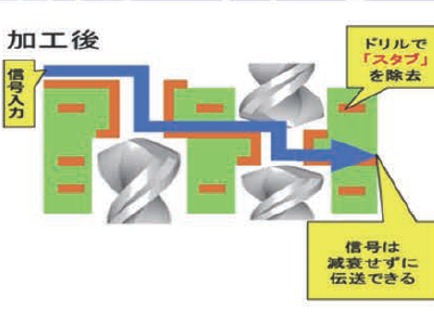

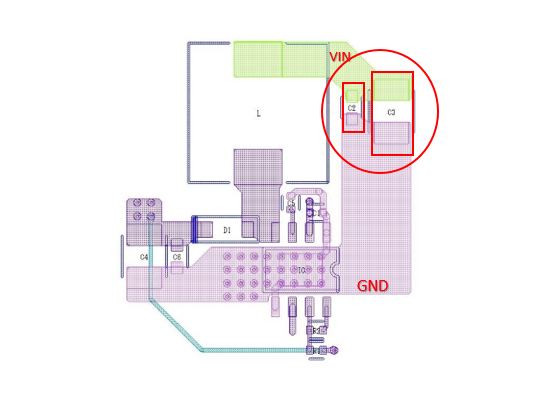

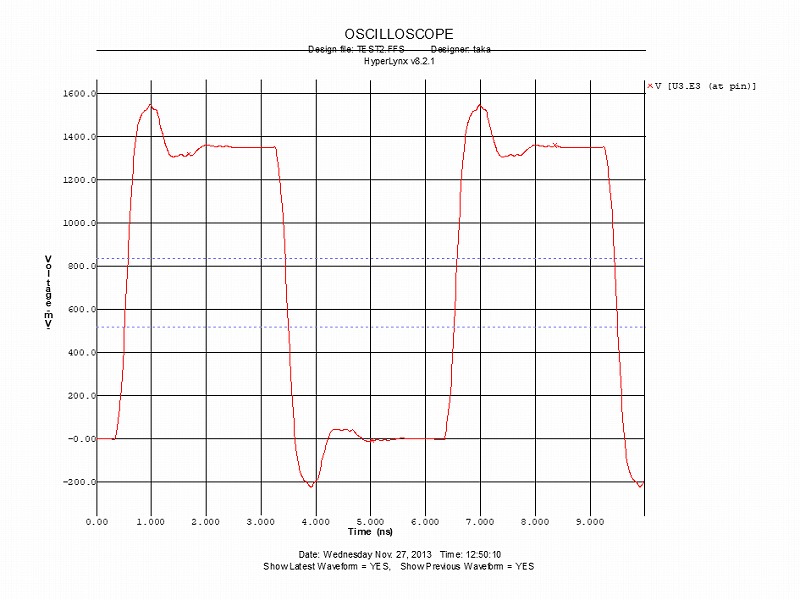

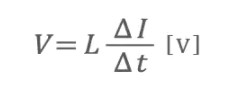

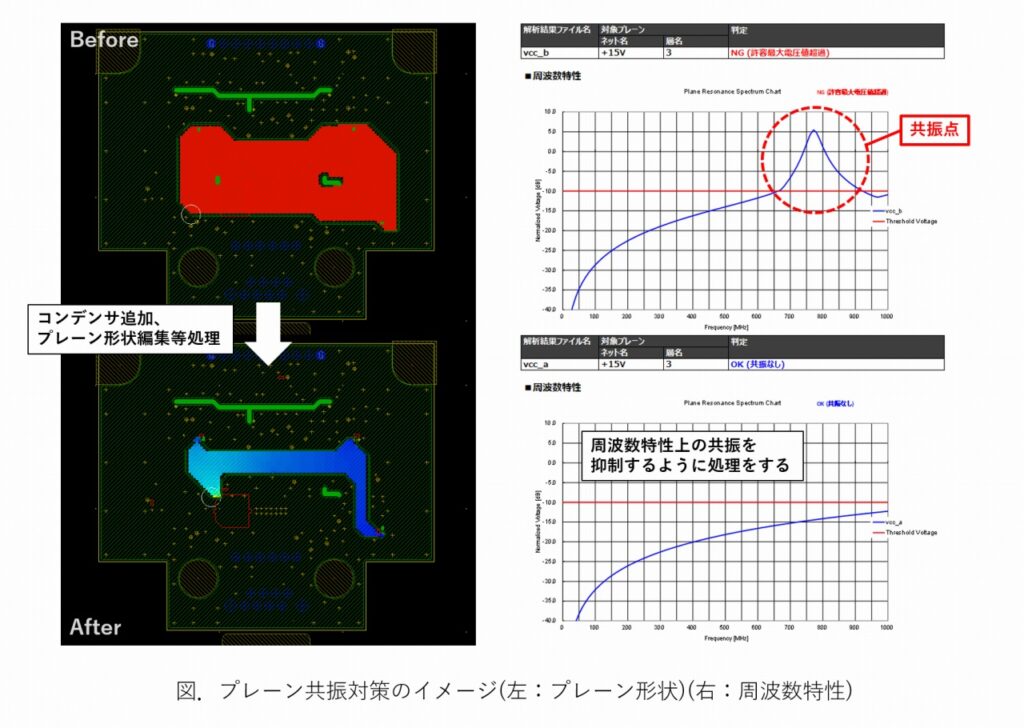

継続して電源プレーンを貼る場合の対策としては、電源プレーンの形状を編集して面積を減らすか、共振が起きるポイントをシミュレーションソフトで特定した上で、そこにコンデンサやスナバ回路などの対策部品/対策回路を追加して共振を抑えられるポイントを探り、本来の回路に反映させる作業が必要になります。

基板上の電源パターンの経路には電流が流れるポイントが決まっており、広い範囲で電源プレーンを張るとどこに電流が流れるか把握しづらくなります。

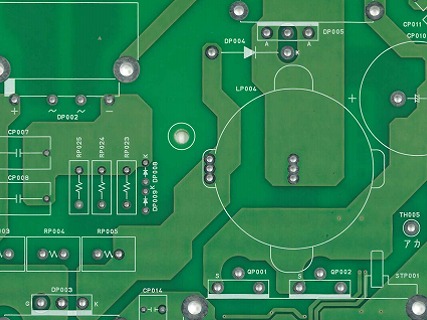

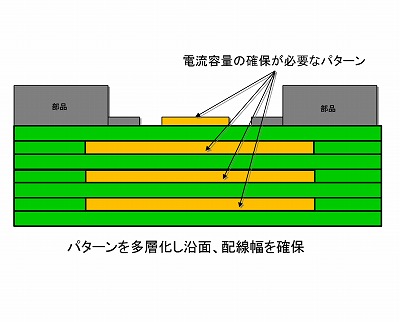

電流が流れる経路をある程度把握しやすくしつつ、電源の配線に利用する空間を減らすために、高周波信号や高速信号を扱う基板では電源プレーンを使わずに初めから線電源を形成して対策することがあります。

面状に形成される電源プレーンに対し、通常の配線と同様に線を引くように配線していく電源パターンの配線を線電源と呼称しますが、線電源については信号線と同等の配線幅ではなく、電流値を考慮して太めの幅で配線することが推奨されます。

また、線電源においてもシミュレーションをかけて共振が起きているポイントに対策部品を挟んで共振を抑制する対策は有効です。