今回の記事では、PCI Expressの基板設計のポイントについて解説いたします。

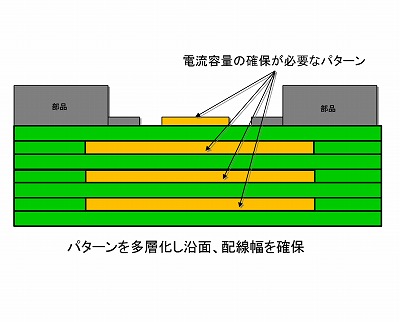

配線幅と層構成

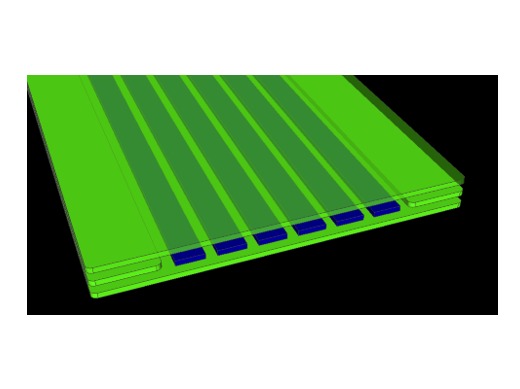

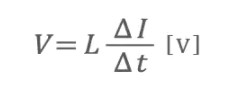

PCI expressの基板設計では転送速度がGHz帯での差動高速配線の為、差動インピーダンスコントロールをする必要があります。年々、PCI Expressの規格や仕様が変更され高速化が加速しています。

転送速度は新しい仕様が出るとそれまでの仕様の2倍の周波数で転送速度が増加してます。配線の高速化進むに連れて、プリント基板の配線設計がシビアになります。インピ―ダンスを一定に制御する必要がある為、配線幅と層構成が重要です。

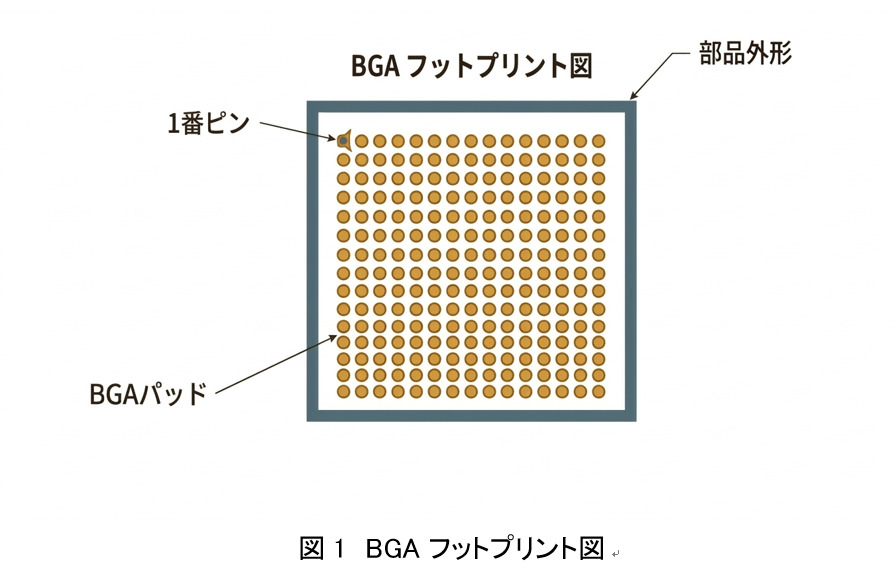

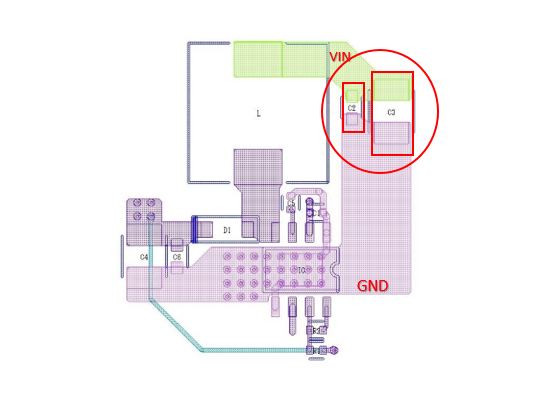

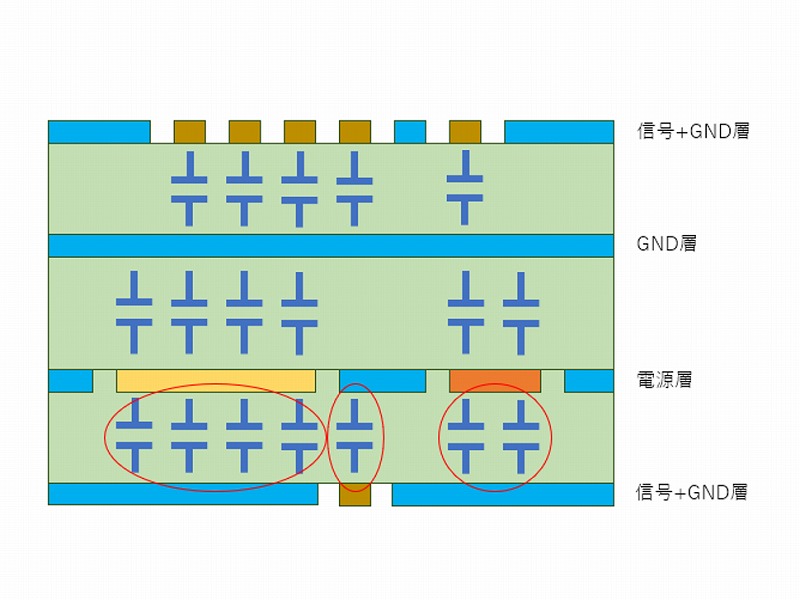

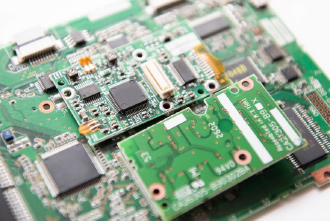

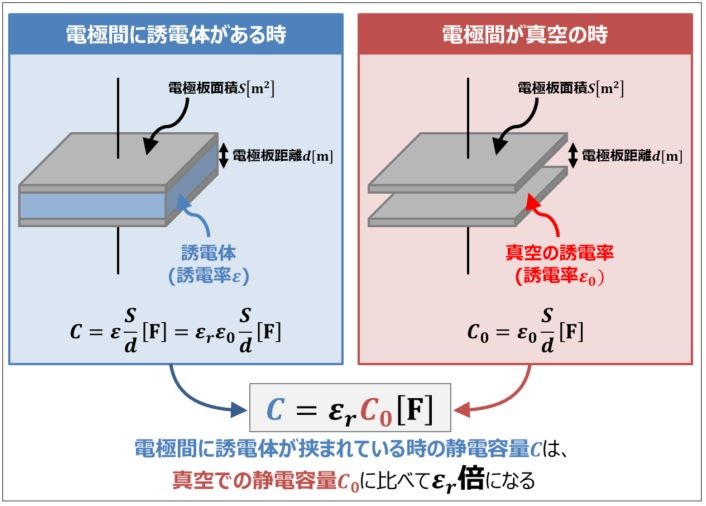

部品のパット部分でインピーダンスが低下し反射が起こるため、なるべくインピーダンスの低下が起こらないようにパット下の銅箔(内層の銅箔)を抜く事でターゲットインピーダンスに近くなるように調整致します。(アンチパットと言います。)

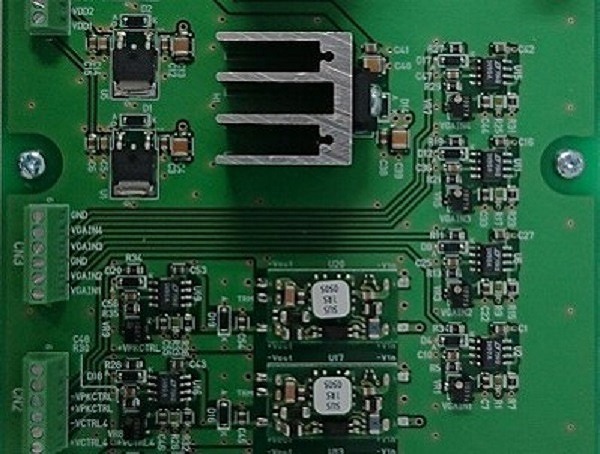

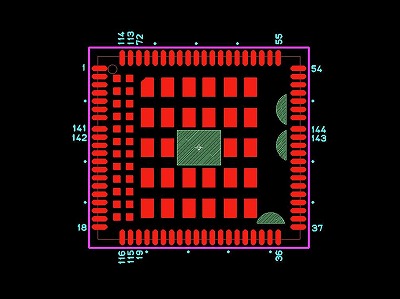

PCI Expressラインの周囲GNDの処理

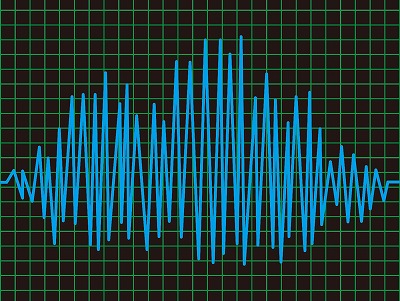

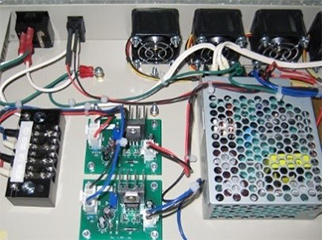

PCIeラインの周囲はGNDで覆う必要があります。PCI ExpressラインとGNDは差動配線幅の4倍~5倍程度距離をとる必要があります。インピーダンスコントロールを行っていますので同層での結合が起こらないようにします。層間の結合でインピーダンスコントロールをします。

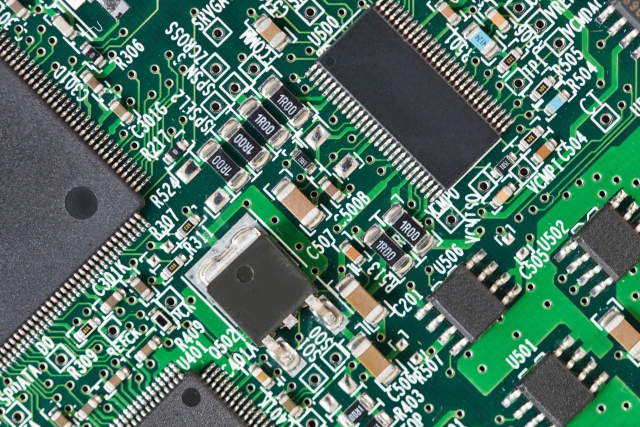

また、GNDのビアも複数配置し周囲を囲みます。そうすることによりGNDのインピーダンスを低下させ、基板の外にノイズを放射しないようにすることが出来ます。また、外部からのノイズの影響も受けにくくなります。GNDビアを配置する事でシールドの効果を上げる事になります。

>>インピーダンスとは?

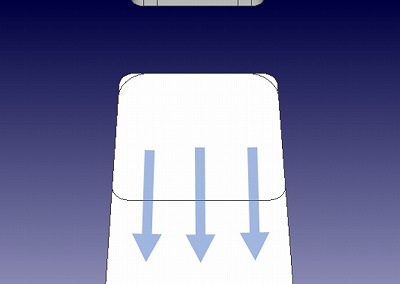

PCI Expressラインのビアのインピーダンス制御

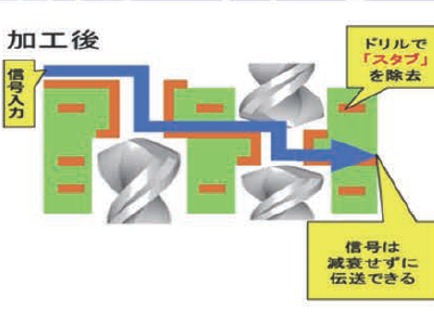

PCI Expressラインの層を切り返すときビアを配置しますがこのビアのインピ―ダンス制御が必要となります。切り返しのビアを打つ事により、その部分がインピ―ダンスが下がってしまう為、極力下がらないようにビアの大きさを小さくする必要があります。

ビアについては基板製造メーカと相談によりサイズを決めることが重要です。PCI Expressラインは差動ラインの為、ビア間も狭い方が良いです。また、基板仕様にもよりますがビアによるスタブも極力無いようにしてください。インピーダンスの変化が反射を引き起こす為、ノイズを発生致します。

PCI Expressラインの差動等長の注意事項

PCI Expressラインは差動配線の為、ペアとなる線の等長する必要があります。配線を曲げる時には45度配線は行わず、必ずR付け配線を行いましょう。45度配線では内側と外側の配線間の距離が離れてしまいインピーダンスが変わってしまします。配線長もR付け配線と比べると配線誤差が若干大きくなってしまいます。ペア配線の配線長調整はTx側でインピーダンスの変化を最小限になるように調整します。

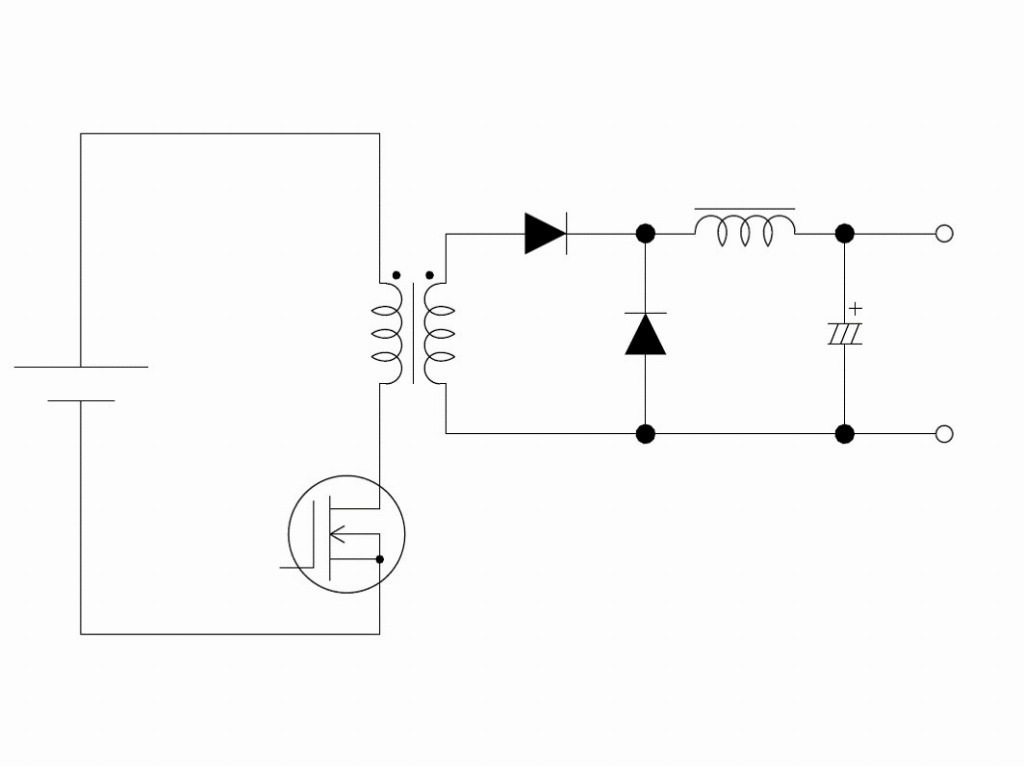

PCI Expressの基板設計:まとめ

PCI Expressライン等、高速信号の基板設計はインピーダンスの変化を抑える事が大事です。急激なインピ―ダンスの低下が起こらないように、使用部品のパットやビア等のインピーダンス制御が必要です。

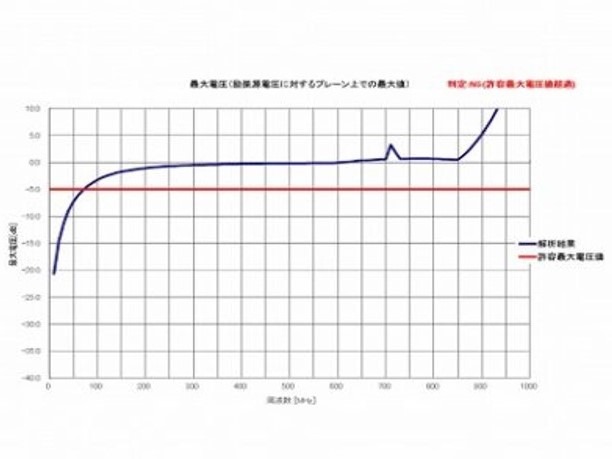

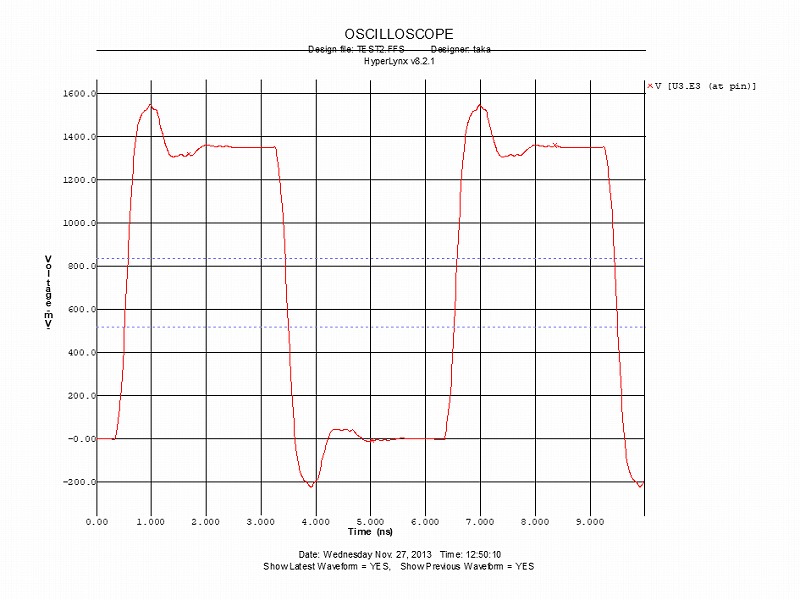

シミュレーションを用いて解析しながら対策を反映し基板設計をして行く必要があります。シミュレーションには電磁界シミュレータを用いて解析をします。TDR測定を行うことでインピーダンスの乱れている箇所も見つけることが出来ます。

>>無料ガイドブック「高周波基板 設計のポイント」はこちら!